## Agile RF Synthesizer & AOM driver

ARF021/ARF421, XRF021/XRF421

Version 1.7.8, Rev 8 hardware

## Limitation of Liability

MOG Laboratories Pty Ltd (MOGLabs) does not assume any liability arising out of the use of the information contained within this manual. This document may contain or reference information and products protected by copyrights or patents and does not convey any license under the patent rights of MOGLabs, nor the rights of others. MOGLabs will not be liable for any defect in hardware or software or loss or inadequacy of data of any kind, or for any direct, indirect, incidental, or consequential damages in connections with or arising out of the performance or use of any of its products. The foregoing limitation of liability shall be equally applicable to any service provided by MOGLabs.

## Copyright

Copyright © MOG Laboratories Pty Ltd (MOGLabs) 2015 - 2022. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying or otherwise, without the prior written permission of MOGLabs.

## Contact

For further information, please contact:

MOG Laboratories P/L 49 University St Carlton VIC 3053 AUSTRALIA +61 3 9939 0677 info@moglabs.com MOGLabs USA LLC 419 14th St Huntingdon PA 16652 USA +1 814 251 4363 www.moglabs.com

## **Preface**

Acousto-optic modulators (AOMs) are an integral part of many laserbased experiments. They are used for frequency shifting, amplitude modulation, and laser frequency stabilisation. Many experiments reguire very simple control of the RF frequency and power, but others require sophisticated sequences. The MOGLabs ARF/XRF agile RF synthesizer provides such complexity with a user-friendly interface. The extraordinary capabilities of the ARF/XRF have not previously been available from any single supplier, let alone in a single unit. Two channels, with direct output of up to 4W per channel. Wide frequency range of 20 to 400 MHz. Arbitrary frequency, amplitude and phase with high resolution. Analogue modulation of each channel, in frequency, amplitude, and/or phase, with 10 MHz bandwidth. Ergonomic front-panel controls, and ethernet/USB interface. Tablemode operation to define complex time-dependent waveform output. All in one box which connects directly to AC mains power and to your AOMs. As you delve into this manual you will uncover more and more capability, but the powerful FPGA at the heart of the ARF/XRF allows software improvements to add new features, so please check the MOGLabs website for updates, example code, and assistance.

We hope that you enjoy using the ARF/XRF, and please let us know if you have any suggestions for improvement in the ARF/XRF or in this document, so that we can make life in the lab better for all.

MOGLabs, Melbourne, Australia www.moglabs.com

## Safety Precautions

Safe and effective use of this product is very important. Please read the following safety information before attempting to operate. Also please note several specific and unusual cautionary notes before using the MOGLabs ARF/XRF, in addition to the safety precautions that are standard for any electronic equipment.

- **CAUTION** To ensure correct cooling airflow, the unit should not be operated with cover removed.

- **WARNING** High voltages are exposed internally, particularly around the mains power inlet and internal power supply unit. The unit should not be operated with cover removed.

- **NOTE** The MOGLabs ARF/XRF is designed for use in scientific research laboratories. It should not be used for consumer or medical applications.

## **Protection Features**

The MOGLabs ARF/XRF includes a number of features to protect you and your device.

Open/short circuit Each RF output should be connected to a  $50\,\Omega$  load. The ARF/XRF will disable each high-power RF output if not connected or if a short-circuit is detected.

**Reflected power** The RF reflected power and VSWR (voltage standing wave ratio) are monitored and RF output is disabled if either exceeds their safe limit settings.

Mains filter Protection against mains transients.

**Temperature** Several temperature sensors control the fan and will trigger a shutdown if the temperature exceeds a safe limit.

# **Contents**

| Pr | eface                                              |                                  |

|----|----------------------------------------------------|----------------------------------|

| Sâ | fety Precautions                                   | ii                               |

| Pr | otection Features                                  | iv                               |

| 1  | Introduction 1.1 Operating modes                   | 1<br>2<br>2                      |

| 2  | Connections and controls  2.1 Front panel controls | E .                              |

| 3  | Communications 3.1 Protocol                        | 11<br>11<br>13<br>14             |

| 4  | MOGRF host software 4.1 Device discovery           | 17<br>17<br>18<br>19<br>24<br>25 |

| 5  | External modulation 5.1 Operational principle      | 27<br>27<br>28                   |

vi

|   | 5.3<br>5.4     | Dual modulation: fast and slow modes Examples | 30<br>31     |

|---|----------------|-----------------------------------------------|--------------|

| 6 | <b>PID</b> 6.1 | ·                                             | <b>35</b> 35 |

|   | 6.2            | PID control loop                              | 36           |

|   | 6.3            | Dual modulation with PID                      | 37           |

|   | 6.4            | Noise-eater implementation                    | 38           |

|   | 6.5            | Example                                       | 39           |

| 7 | Digi           | ital I/O                                      | 41           |

|   | 7.1            | DE15 connector                                | 41           |

|   | 7.2            | High-speed digital                            | 43           |

|   | 7.3            | XSMA breakout board                           | 45           |

|   | 7.4            | Configuration                                 | 46           |

|   | 7.5            | TTL switching                                 | 48           |

|   | 7.6            | Pulse generation                              | 49           |

|   | 7.7            | Counters                                      | 51           |

|   | 7.8            | Examples                                      | 52           |

| 8 | Sim            | ple table mode                                | 55           |

|   | 8.1            | Operational principle                         | 55           |

|   | 8.2            | Defining table entries                        | 56           |

|   | 8.3            | Digital I/O                                   | 59           |

|   | 8.4            | Loops and triggers                            | 63           |

|   | 8.5            | Upload and download                           | 67           |

|   | 8.6            | Re-arm and restart                            | 68           |

|   | 8.7            | Linear ramps                                  | 69           |

|   | 8.8            | Synchronous table execution                   | 71           |

| 9 | Adv            | anced table mode (XRF)                        | <b>7</b> 3   |

|   | 9.1            | Operational principle                         | 73           |

|   | 9.2            | Defining table entries                        | 74           |

|   | 9.3            | Initial and final states                      | 78           |

|   | 9.4            | Counters                                      | 79           |

|   | 9.5            | Loops and triggers                            | 80           |

|   | 9.6            | Linear ramps using extrapolation              | 81           |

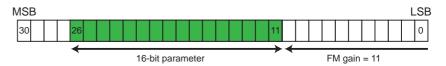

|   | 9.7            | Frequency gain                                | 83           |

*Contents* vii

| 9.8<br>9.9                                                                  | Other instruction parameters                                                                                                                                                                        | 85<br>86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spe                                                                         | •                                                                                                                                                                                                   | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

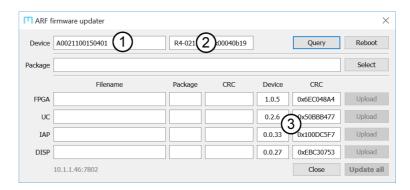

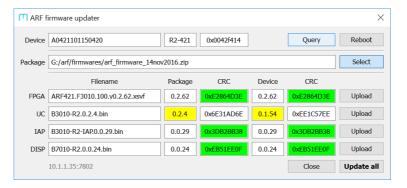

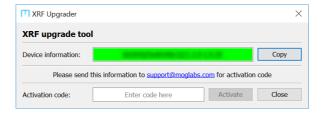

| Firm<br>B.1<br>B.2<br>B.3<br>B.4<br>B.5                                     | Firmware components                                                                                                                                                                                 | 93<br>93<br>94<br>94<br>97<br>98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| C.1<br>C.2<br>C.3<br>C.4<br>C.5<br>C.6<br>C.7<br>C.8<br>C.9<br>C.10<br>C.11 | Arguments General functions Basic control Primary RF control Modulation Digital ramp generator Monitor outputs Clock reference Table mode PID feedback External IO functions Configuration settings | 99<br>99<br>100<br>101<br>103<br>106<br>107<br>108<br>109<br>113<br>115<br>117<br>118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

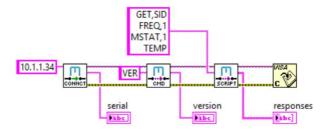

| D.1<br>D.2<br>D.3<br>Trou<br>E.1<br>E.2<br>E.3<br>E.4<br>E.5                | python                                                                                                                                                                                              | 121<br>123<br>124<br>125<br>125<br>125<br>126<br>126                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                             | 9.9 <b>Spe</b> (Firm B.1 B.2 B.3 B.4 B.5 <b>Com</b> C.1 C.2 C.3 C.4 C.5 C.6 C.7 C.8 C.9 C.10 C.11 C.12 C.13 <b>Cod</b> D.1 D.2 D.3 <b>Trou</b> E.1 E.2 E.3 E.4                                      | Specifications  Firmware upgrades B.1 Firmware components B.2 Factory reset B.3 Upgrade via mogrffw B.4 Upgrade via web interface B.5 Upgrading an ARF to an XRF  Command language C.1 Arguments C.2 General functions C.3 Basic control C.4 Primary RF control C.5 Modulation C.6 Digital ramp generator C.7 Monitor outputs C.8 Clock reference C.9 Table mode C.10 PID feedback C.11 External IO functions C.12 Configuration settings C.13 Direct DDS control  Code examples D.1 python D.2 matlab D.3 LabVIEW  Troubleshooting E.1 Computer interface E.2 Unexpectedly high output power E.3 Incorrect output power E.3 Incorrect output power E.4 No RF output power E.5 CHx-OFF has no effect |

viii Contents

## 1. Introduction

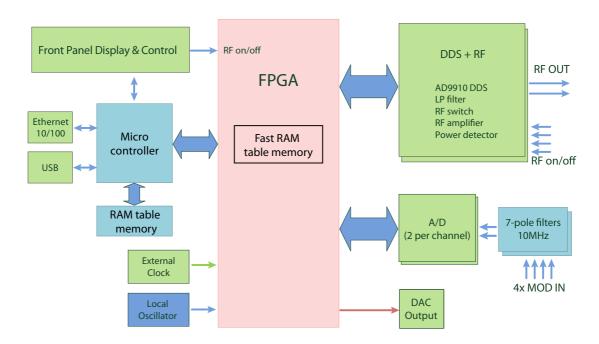

The MOGLabs ARF/XRF consists of two independent AD9910 direct digital synthesizer (DDS) sources, each with 4W amplifier. The frequency, amplitude and phase of each output is software-controlled via a microcontroller and FPGA (field programmable gate array). This enables direct control of the frequency, amplitude and phase of the RF signals, which can be adjusted in real-time using the front-panel control knobs, or via a scripting language over ethernet or USB. The RF parameters can be defined in a lookup table (loaded via ethernet or USB) to enable complex sequences with very fast transitions.

The block diagram below shows the key components. The RF signal output from each DDS is low-pass filtered, pre-amplified, and

then further amplified with a GaN hybrid high-power output stage (ARF421/XRF421 only). The RF signals are monitored to check output power and to measure the reflection (VSWR).

The DDS chips are controlled by the FPGA. A microcontroller provides external interface with TCPIP and USB communications, and controls the front-panel display, rotary encoders (knobs) and push-buttons.

The device allows analogue modulation through two analogue-to-digital converters (ADC) with anti-aliasing filters. When modulation is enabled, the FPGA periodically reads the value of the modulation signal and uses that value to reprogram the DDS frequency, power and/or phase.

The ARF/XRF includes memory for storing complex waveform sequences, where each step in the sequence can include frequency, power, phase, time delay, and more complex definitions of ramps and other time-dependent functions. Complex capabilities can be accessed via either TCPIP or USB communications. See Chapter 3 for information on communications options and setup.

Once communications are established, the ARF/XRF can be controlled with simple text commands. The commands can be very basic, for example to define the frequency or power, or they can define complex dynamic sequences. Appendix C provides a summary of the available commands.

### 1.1 Operating modes

The ARF/XRF can be used at varying levels of complexity, as either a free-running RF source or to follow pre-determined instructions defined in a table. The modes of operation are outlined below, and the current operational mode of each channel can be individually set using the MODE command.

#### NSB: Basic mode

Default state on power-up. In this mode, each channel acts as a simple single-frequency RF source, with the DDS chips controlled directly by the FPGA. The frequency and power of the signal can be controlled via the front panel, using simple instructions over the computer interface (e.g. FREQ or POW), or using the modulation inputs. Basic mode is convenient for driving AOMs and other single-frequency devices, with the flexibility of modulation and PID control.

#### NSA: Advanced mode

Advanced mode provides direct user-control of each DDS through its internal registers via the DDS command. Direct programming of each DDS is complex and not necessary for most applications; it requires careful reference to the AD9910 datasheet and manual calculation of the hardware registers.

### TSB: Simple table mode

In table mode, the RF parameters are automatically sequenced by the FPGA according to a table of values pre-loaded by the microcontroller and stepped through automatically. The table entries are defined by simple text commands from the host computer which define the RF frequency, amplitude, phase and any I/O behaviour, as detailed in chapter 8. The minimum duration of a TSB entry is 1  $\mu s$  and each table can comprise up to 8191 instructions.

#### TPA: Advanced table mode

XRF models provide a more advanced table mode with greatly improved timing resolution and single parameter updates at 16 ns intervals. Smooth pulses can be generated with precise control of the envelope through piecewise-linear interpolation. Details on advanced table mode functionality are described in chapter 9.

### 1.2 Feature compatibility

The ARF/XRF provides a wide range of functionality, but not all features are compatible with each other. The following table summarises which features can be used in which modes.

|                                | NSB | NSA | TSB | TPA |

|--------------------------------|-----|-----|-----|-----|

| Front-panel controls           |     | X   | X   | X   |

| External modulation (AM/FM/PM) | 1   | X   | X   | X   |

| PID control                    | 1   | X   | X   | x   |

| Direct TTL on/off control      | 1   | 1   | X   | X   |

| Direct DDS control             | X   | 1   | X   | X   |

| Autonomous execution           | X   | X   | 1   | 1   |

| External TTL trigger           | X   | X   | 1   | 1   |

| TTL output                     | ✓   | 1   | 1   | 1   |

**Table 1.1:** Summary of feature compatibility

## 1.3 RF on/off control

The RF output can be turned on and off via software control of the DDS generators, but for many applications that is too slow and the extinction ratio is inadequate. The ARF/XRF has additional hardware-based on/off control on the output of each DDS, using an RF switch before the amplifiers.

This hardware switch short-circuits the RF output of the DDS, and can be controlled via a combination of software and hardware inputs (see  $\S7.6$ ). In this way, the RF can be controlled using the front panel, the ON/OFF commands, as well as via table entries.

There is additional control of the DC supplies to the high-power RF amplifiers to further improve the extinction ratio. The response time is significantly longer than just switching the RF signal, but reduces the RF noise on the output.

## 2. Connections and controls

### 2.1 Front panel controls

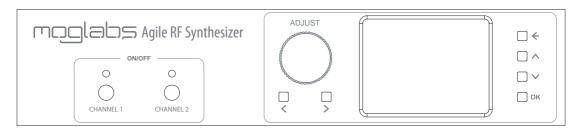

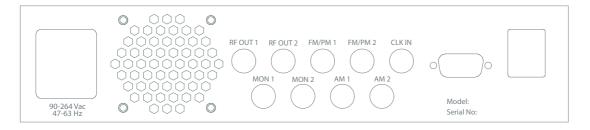

**Figure 2.1:** Front-panel layout of REv8 ARF/XRF devices. Other revisions may have a different appearance.

Starting with Rev6 devices, the front-panel includes an interactive menu system for controlling the device. The buttons on the right-hand side of the display navigate through the menu structure, while the encoder wheel is used to edit values. The  $\land$  and  $\lor$  keys change between menu items,  $\leftarrow$  exits to the previous menu, and OK enters the selected menu or activates the selected command.

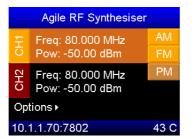

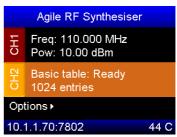

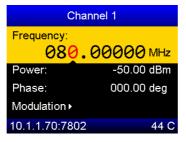

The main menu (Figure 2.2) shows the current mode and status of each channel. In basic (NSB) mode, the current frequency and power of each channel is displayed, as well as whether modulation is currently enabled. Pressing the OK button with a channel selected will open the sub-menu to adjust settings for that channel (Figure 2.3).

The color of each menu item represents its purpose, as listed below.

White Static value, displayed for diagnostic purposes.

Yellow Adjustable value, modified using the encoder wheel.

**Orange** Currently selected channel.

Blue Submenu, entered with the OK button.

**Green** Command, executed by the OK button.

**Figure 2.2:** The main menu shows the current state of each channel. Left: both channels are in basic mode, with AM and FM enabled on CH1, and PM enabled on CH2. Right: CH2 is in basic table mode, with the number of entries in the table shown.

**Figure 2.3:** The basic parameters of each channel can be edited directly. Turning the encoder wheel modifies the selected digit of the current value (left) as indicated by the arrow. Pressing the encoder wheel changes to *digit select mode* (right), allowing the selected digit to be changed by turning the encoder.

| Ethernet Settings |               |  |

|-------------------|---------------|--|

| Current IP:       | 10.1.1.70     |  |

| Static IP:        |               |  |

| 10.               | 1.1.190       |  |

| IP Mask:          | 255.255.255.0 |  |

| Gateway:          | 10.1.1.1      |  |

| 10.1.1.70:7802    | 44 C          |  |

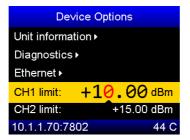

**Figure 2.4:** The options menu allows configuration of various settings, such as the maximum output power (left) and ethernet options (right).

7

When an editable (yellow) value is selected, turning the encoder wheel changes the value of the selected digit as identified by the arrow and red text. To change the digit of interest, either use the < or > buttons (Rev8+) or press the encoder wheel to change to *digit selection mode*. In this mode, the currently selected digit is shown on a black background, and is changed by turning the encoder wheel. Pressing the encoder again returns to *value modification mode*.

The options menu (Figure 2.4) allows the device configuration to be adjusted. In particular, the power limit applied to each channel should be set as per the desired application before use (see also the LIM command). The ethernet settings of the device can also be set using this interface, including whether to enable DHCP and the fall-back static IP address of the device. When in use, the network status is displayed on the display footer, and once connected displays the current IP address. Note that the "Restart ethernet" command must be used before changes in the ethernet menu will take effect.

Each channel of the device can be turned on or off using the pushbuttons on the left of the front-panel. Each channel also has an associated multi-colour status LED indicator whose colour shows the current output state of the channel as follows.

| Colour | DDS signal  | Amplifiers |  |

|--------|-------------|------------|--|

| Off    | X           | Х          |  |

| Green  | 1           | ✓          |  |

| Yellow | 1           | X          |  |

| Blue   | ×           | ✓          |  |

| Purple | Debug mode  |            |  |

| Red    | Error state |            |  |

The overall brightness of the display can be set with the "contrast" value in the Options menu. The display also includes a "sleep" timer that dims the display if it hasn't received input in a given period of time. This feature can be disabled by setting the sleep timer value to 0.

## 2.2 Rear panel controls and connections

- **IEC power in** The ARF is compatible with all standard AC power systems, from 90 to 264 V and 47 to 63 Hz. The maximum current draw is about 1 A.

- Fan The ARF has three temperature-controlled fans directing air flow over the RF power amplifiers and the FPGA, exhausting through the rear vent. Ensure that the vent does not become blocked.

- RF OUT SMA connectors for the primary RF outputs. Should be connected to a  $50\Omega$  load. Must not be short-circuited.

- MON SMA connectors for "monitor" RF outputs, which are  $-20\,\mathrm{dBc}$  copies of the main output (when high-impedance terminated).

- AM/FM/PM SMA analog inputs, nominally for frequency and amplitude modulation (see chapter 5). These inputs can also be used for laser noise-eater or frequency stabilisation applications (see chapter 6).

- CLK IN The ARF can be synchronised to a high-performance external clock input via this SMA connector and software commands (see §C.8). The input is  $50\,\Omega$  terminated, and the provided reference should be between  $+3\,\mathrm{dBm}$  and  $+10\,\mathrm{dBm}$ , and preferably square-wave.

- DE15 The DE15 connector provides basic I/O functionality (§7.1). There are TTL inputs for quickly suppressing the RF output, and TTL outputs for controlling experimental devices such as shutters. Two general-purpose analogue outputs are also available for monitoring purposes.

9

The XSMA breakout board is available to provide convenient SMA connectors for each I/O channel (§7.3).

RJ45/USB-A Ethernet (TCP/IP 10/100 Mb/s) and USB communications jacks.

#### Internal DIP switches 2.3

Four DIP switches are provided to assist in diagnosis and recovery of the ARF/XRF units. They should be left in default configuration for regular operation.

**WARNING** There is potential for exposure to high voltages inside the ARF/XRF. Take care around the power supply and ensure that objects, particularly electrically conducting objects, do not enter the unit.

CAUTION

The cover should be replaced before powering on to ensure proper airflow and cooling.

|   | OFF                  | ON                   |

|---|----------------------|----------------------|

| 1 | Normal operation     | Firmware update mode |

| 2 | Disable FPGA         | Normal operation     |

| 3 | Use factory settings | Normal operation     |

| 4 | Normal operation     | Factory reset        |

- Default OFF. If switched ON, the unit will start in firmware upload DIP 1 mode (see §B.3).

- **DIP 2** Default ON. Switch OFF to disable the FPGA for diagnostic purposes.

- **DIP 3** Default ON. Switch OFF to use default device and network settings.

- DIP 4 Default OFF. Switch ON and reboot to restore the unit to factory version and configuration.

## 3. Communications

The ARF can be connected to a computer by USB or ethernet (TCPIP). The software package mogrf (chapter 4) provides interactive functionality, or communications can be integrated into existing control software. Examples of controlling the ARF/XRF in several languages are provided in Appendix D.

#### 3.1 Protocol

Communication follows a query/response protocol, where the user sends an ASCII string to the unit, and the unit sends an ASCII response back. The list of possible commands is detailed in Appendix C. All messages are CRLF-terminated, requiring that any communications must end with a carriage return ('\r' = ASCII 0x0D) and new-line ('\n' = ASCII 0x0A). Most terminal applications and drivers provide the ability to automatically append these characters when configured appropriately.

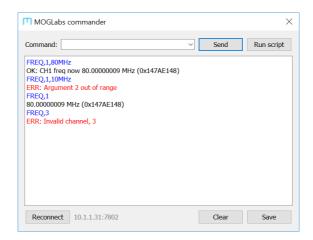

Statements are either "commands" or "queries". A command is a statement that causes some action to occur, and the unit will respond with either "OK" or "ERR" depending on whether the command succeeded or not. For example,

- > FREQ,1,80MHz

- < OK: CH1 freq now 80.00000009 MHz (0x147AE148)

- > FREQ,1,10MHz

- < ERR: Frequency 10.00 MHz out of range

The response describes the outcome of the command, such as the achieved frequency taking into account discretisation by the DDS.

Queries are statements that return a value, which respond with the value in physical units first where applicable, or an error message beginning with "ERR". For example,

- > FREQ,1

- < 80.00000009 MHz (0x147AE148)

- > FREQ.3

- < ERR: Invalid channel, 3

In the above example, the frequency query provides a value first in MHz as well as the internal DDS setting (called the "frequency tuning word") as hexadecimal in brackets.

It is strongly recommended that all software should wait for this response and check whether it indicates an error before continuing. The python and LabVIEW bindings provided by MOGLabs take care of buffering and error checking automatically.

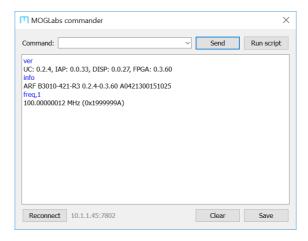

The "mogcmd" application, which is available from the MOGLabs website as a standalone application or as part of the mogrf package, provides a convenient interface for sending commands and receiving responses (Figure 3.1).

**Figure 3.1:** The mogcmd application, showing successful and unsuccessful commands and queries.

3.2 TCP/IP 13

### 3.2 TCP/IP

The ARF/XRF can be accessed over ethernet via the IPv4 protocol. When ethernet is connected, the ARF will attempt to obtain an IP address by DHCP. If DHCP fails, an internally defined address will be used. In both cases, the address will be shown on the device display (for example, 10.1.1.190:7802), showing the address and port number for communicating with the device.

## 3.2.1 Changing IP address

Depending on your network settings, you may need to manually set the IP address. This is most easily done via the front-panel interface in Rev6 + devices as follows. Once configured, these settings are stored in the non-volatile memory of the unit and will be recalled in future. However, automatic address acquisition via DHCP is a simpler solution where available.

- 1. From the main menu, open Options > Ethernet Settings.

- 2. Select "Static IP" and use the encoder wheel to set the IP address of the device as required. Note that pressing the encoder wheel changes between octets of the address.

- 3. Select "Gateway" and set the gateway address as required.

- 4. Select "DHCP" and set to OFF by turning the encoder anticlockwise.

- 5. Select "Restart ethernet" and press the OK button.

- 6. The new IP address will be displayed in the display footer.

In some situations it may be necessary to power-cycle the device to propagate ethernet changes.

#### 3.3 USB

The ARF/XRF can be directly connected to a host computer using a USB cable (type A-male). The device will appear as a Virtual COM port - a fast serial port that behaves like an RS232 connection.

The required STM32 Virtual COM Port Driver (VCP) device driver is available from the MOGLabs website for the Windows<sup>TM</sup> operating system. After installation, the ARF/XRF will appear as a new COM port on the machine.

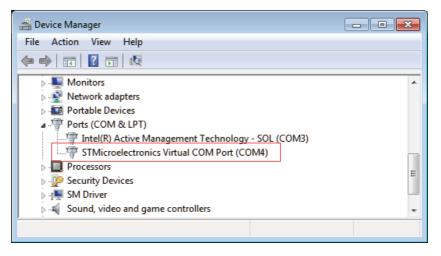

To determine the port number of the device, go to Device Manager (Start, then type Device Manager into the Search box). You should see a list of devices including "Ports" (Figure 3.2).

**Figure 3.2:** Screenshot of Device Manager, showing that the ARF can be communicated with using COM4. The port number might change when plugging into a different USB port, or after applying a firmware update.

The device can be identified as a COM port with the following name, STMicroelectronics Virtual COM Port (COMxx) where xx is a number (typically between 4 and 15). In the example above, the device was installed as COM4.

*3.3 USB* 15

Note that if the port appears in Device Manager with a different name, then the driver was not successfully installed. If this occurs, disconnect the device from the host computer, reinstall the VCP driver, then reconnect the USB cable.

The mogrf host software (§4) automatically enumerates the available COM ports when started, making device identification simpler.

## 4. MOGRF host software

The mogrf software package provides a simple user interface to the basic behaviour of ARF/XRF devices, with the ability to issue commands, run scripts, control tables, and apply firmware updates.

**Please note:** It may be necessary to install a firmware update (see Appendix B) to use the software described in this section.

### 4.1 Device discovery

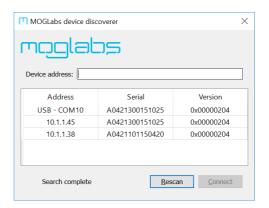

Upon starting the application, a device discoverer (Figure 4.1) is initiated. This program scans the COM ports of the host computer looking for an ARF/XRF device, and then scans the local network subnet. Starting the application is then as simple as selecting the device and clicking *Connect*. If your device is not listed, recheck your connection and network settings.

If the network and/or firewall blocks device discovery, enter the IP address of the unit in the *Device address* box directly.

**Figure 4.1:** Example of the *Device discoverer* window, showing that one USB device and two networked devices were detected.

#### 4.2 Device commander

The *Device commander* is an interactive terminal for issuing commands and queries to your ARF/XRF device and displaying the result (Figure 4.2). The accepted commands and their functions are listed in Appendix C. Type statements into the *Command* box and execute them by pressing the ENTER key or clicking Send. The window contains a history of recently executed commands.

**Figure 4.2:** The *Device commander* window, which permits the execution of individual instructions or of text files containing scripts.

Scripts are ASCII text files where each line corresponds to a command to be executed (see Appendix D). Clicking Run script triggers stepwise execution of such a script, where the success of each statement is checked before executing the subsequent line. If an error occurs, execution of the script is aborted and an error message is displayed.

If the device is restarted or the connection is lost, clicking *Reconnect* will attempt to reestablish communication.

### 4.3 MOGRF main window

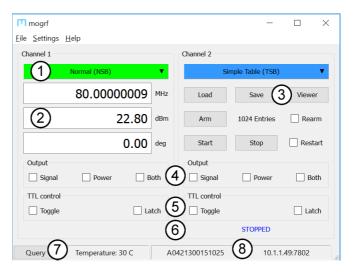

The main window of mogrf is shown below. The two channels are displayed side-by-side, with information and controls that depend on the current operational mode of each channel.

**Figure 4.3:** The main window of mogrf, showing Channel 1 in normal (NSB) mode and Channel 2 in simple table (TSB) mode.

The main features of the application are as follows:

- Current operational mode of the channel. Click to change mode by selecting from a list. Note that "advanced table mode" will only appear on XRF units.

- 2. Current frequency, amplitude and phase in NSB mode. Changing the value immediately updates the output.

- 3. Controls are provided for specific table-mode functionality. Tables can be exchanged with internal FLASH memory, or uploaded/downloaded from the host machine in binary or CSV format (§8.5). Table execution can be started or stopped, auto-restart configured (§8.6), and a graphical viewer is provided for table visualisation in TSB mode (§4.4).

- 4. Channel output can be controlled by enabling only the RF switch (signal), RF amplifiers (power) or both (421-series only).

- 5. Options to enable external TTL control of the channel output using the OFF input on the DE15 connector (see §7.6).

- 6. Current channel status. Includes whether any modulation options are enabled (both frequency and amplitude modulation are enabled in this example) and the current execution status in table mode.

- 7. Click *Query* to manually update the displayed status information. Useful for reflecting changes caused by device commands or front-panel input.

- 8. The status bar contains diagnostic information about the unit and connection.

#### 4.3.1 File menu

### Device command

Starts the *Device commander* (§4.2) for interactive execution of instructions to control the device.

### Upload firmware

Starts the firmware update application to upload and install updates on the device. The procedure for applying firmware updates is described in detail in Appendix B. It is strongly recommended to make a backup of device settings (Settings → Download settings) before commencing an update.

Upload table Upload a previously downloaded binary table to FLASH memory, which can be subsequently loaded into either channel. Note that binary compatibility between firmware revisions is not quaranteed, and it is recommended that all tables be generated and stored in ASCII (human-readable) form.

21

#### 4.3.2 Settings menu

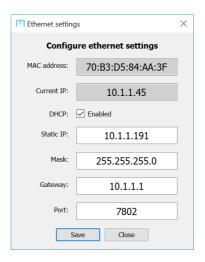

**Ethernet** Allows configuration of network connection settings (IP address, mask, gateway and port). Particularly useful for configuring the network settings over USB. Note that changing the *Static IP* only has an effect if DHCP is disabled, or if DHCP name resolution fails.

**Figure 4.4:** Ethernet configuration interface.

Note that changing the ethernet settings will require the application to be restarted, and may also require the device to be rebooted. The port should be unchanged at 7802 to ensure that the mogrf suite of programs can continue to communicate with the device.

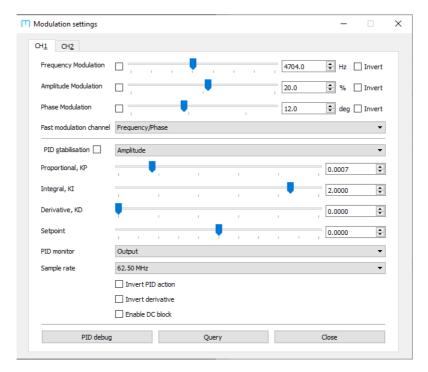

Modulation

The ARF/XRF supports a wide variety of modulation options, as detailed in chapter 5. Individual modulation types can be enabled/disabled and their gains adjusted (Figure 4.5).

**Synchronisation** Configures the channel synchronisation feature, detailed in §8.8.

MOD Out

Select a monitoring signal to output on the CHx-AOUT pin of the DE15 connector. Potential signals are described in the documentation for the MOUT command.

**Figure 4.5:** Use the Modulation dialog in the mogrf application to change the modulation settings for each channel

### Download settings

Downloads configuration and calibration data from the device and stores it in a file for backup purposes. It is strongly recommended to download settings before applying firmware updates.

Upload settings Restore previously downloaded settings to the unit.

### 4.3.3 Help

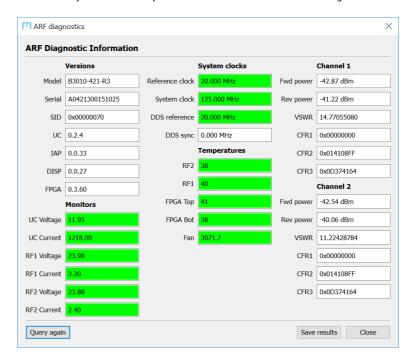

Diagnostics

Queries the unit for diagnostic information, which may be useful in assessing issues with the functionality of the ARF/XRF (Figure 4.6). When encountering a problem with the device, please run the diagnostics and click "save results". Please send the resulting text file and a description of the problem to MOGLabs for analysis.

**Figure 4.6:** Diagnostic information about the connected ARF unit, which should be sent to MOGLabs for analysis if there is a problem with the device.

**About** Displays version information about the mogrf toolkit and connected ARF/XRF device, for support purposes.

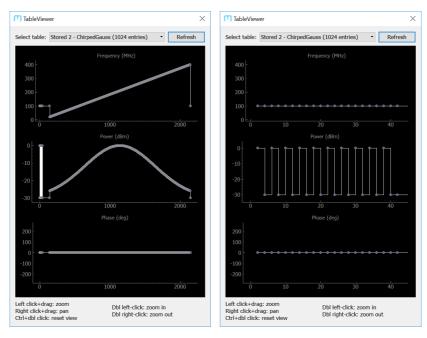

### 4.4 Table viewer

In simple table mode (TSB mode), mogrf provides a viewer for inspecting both the table instructions currently loaded into each channel, as well as the instructions stored in FLASH memory (Figure 4.7). This is beneficial for cataloguing the sequences in memory, as well as for debugging sequences which have been generated by scripts and uploaded to the device.

**Figure 4.7:** *Table viewer* showing how the frequency, power and phase of a table stored in FLASH memory change across the sequence (left). The example shown is a chirped Gaussian pulse, with a number of rapid on/off pulses at the beginning. Mouse controls allow zooming in on areas of interest, such as the rapid pulses at the start of the sequence (right).

At present, the table viewer is only available for simple tables, but may be extended in future to provide visualisation of advanced tables. Also, table viewer may not work correctly over USB due to the reduced communication speed of the virtual COM port interface.

## 4.5 External I/O settings

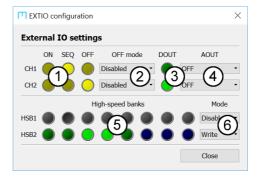

The ARF/XRF provides extensive digital I/O capability through the EXTIO command and configuration window (Figure 4.8). It displays the current input and output state of the I/O pins on both the DE15 connector (§7.1) and the high-speed banks (§7.2). This is to diagnose the I/O state, and that any settings are correct for the desired application. In particular, note that associated pins must be set to "AUTO" control to be used in table mode.

**Figure 4.8:** External I/O configuration window, showing the current state of inputs (yellow), outputs (green), table-mode outputs (blue) and disabled outputs (black). Left-clicking on an output changes its state, and right-clicking brings up a menu of options.

Features of the EXTIO configuration window are:

- 1. Current state of the input pins of the DE15 connector (note that SEQ is disabled on Rev2 units).

- 2. Configure the CHx-OFF input on the DE15 connector as an interlock ("Latch" mode) or for direct control of the RF switch ("Toggle" mode), see §7.6.

- 3. Current state of the DE15 digital output ("shutter") pin, which can be set manually or placed in "Auto" mode to use in table mode.

- 4. Analog monitoring signal currently output on the analog output pin of the DE15 connector.

- 5. Current state of the two high-speed banks. The banks are disabled (black) on boot, and must be set to either read (yellow) or write (green) mode on a per-bank level. However, individual output pins can be set as "Auto" (blue) for use in table mode by right-clicking each indicator.

- 6. Mode to apply to the associated high-speed bank. Note that "Read" mode is not available on Rev2 units.

# 5. External modulation

The ARF/XRF supports external modulation of the RF in NSB mode through the modulation input SMA connectors on the back-panel. Frequency, amplitude and phase modulation of the RF are supported, and dual-modulation is possible for simultaneous FM/AM or FM/PM.

WARNING: The modulation inputs are nominally  $\pm 1V$ , and can be permanently damaged by applying higher voltages. Ensure that modulation is disabled when disconnecting the back-panel SMA connectors, as floating inputs can cause unexpected results.  $50\Omega$  termination is recommended when not in use.

# 5.1 Operational principle

Modulation is performed by digitising the analogue input signal, which is then multiplied by the modulation gain and added to the internal control value associated with the particular modulation mode ("frequency tuning word" for frequency, "amplitude scale factor" for power or "phase offset word" for phase). Limits are applied to the value to ensure that the power is always limited to the value set with the LIMIT command.

The ADC operates at  $62.5\,\text{MS/s}$  with 12-bit resolution ( $\pm 1\,\text{V}$  range), anti-aliased with  $7^{\text{th}}$ -order filters for a measured 3-dB bandwidth of 10 MHz. Simultaneous modulation of two parameters is possible, although one mode will have a reduced bandwidth (see §5.3).

Modulation is enabled/disabled with the MDN command. For example, to enable AM on channel 1, use the command MDN,1,AMPL,ON. Modulation is not available in table mode.

Note: Phase modulation uses the "FM/PM"/"FREQ" input SMA connector.

# 5.2 Modulation gain

The modulation depth is controlled by the "gain" and is set using the GAIN command. Each modulation mode (amplitude, frequency or phase) has a separate modulation gain for individual control, and can be negative to indicate that the modulation action is inverted. The gain can be specified either with physical units, or using an integer representation.

### 5.2.1 Physical units

Since firmware v1.6.4 the gain can be specified with physical units, which corresponds to the modulation achieved at +1V input. Frequency can be specified in MHz, kHz or Hz, phase in degrees or radians, and amplitude in percentage.

For example, when +1V is applied to the associated modulation input, GAIN,1,FREQ,10MHz will shift the output frequency by 10 MHz and GAIN,1,AMPL,-100% will bring the amplitude to zero.

Note changing the output power changes the amplitude and hence the modulation depth as a percentage, so the amplitude gain command must be issued again to keep the percentage depth the same.

Also, when performing frequency modulation, the gain should be chosen so that the output frequency stays between 20 MHz and 400 MHz to prevent unexpected behaviour.

# 5.2.2 Integer representation

The gain is alternatively specified as a signed 32-bit integer in either decimal or hexadecimal, with a negative value indicating the the modulation action is inverted<sup>1</sup>. The range of gain values is shown in the table below.

<sup>&</sup>lt;sup>1</sup>Negative hexademical values are represented using two's complement.

|                | FM            | AM         | PM               |

|----------------|---------------|------------|------------------|

| Max gain (hex) | 0x3FFF8000    | 0x3FFF     | 0xFFFF           |

| Max gain (dec) | 1,073,709,056 | 16,383     | 65,535           |

| Step size      | 0.23 Hz       | 0.006% Max | $0.0055^{\circ}$ |

| Max modulation | 250 MHz       | 100% Max   | 360°             |

**Table 5.1:** Gain ranges for different modulation modes.

Based on these values and ignoring discretisation and saturation, an applied voltage will have the following effective modulation:

Frequency:

$$df = (0.23 \text{ Hz/V})G_f V_{\text{in}}$$

$$Phase: \qquad d\phi = (0.0055^\circ/\text{V})G_\phi V_{\text{in}}$$

$$Amplitude \ (^*): \qquad dA \approx \begin{cases} (14 \text{ V/V})G_a V_{\text{in}} & \text{for 421-models} \\ (2.6 \text{ V/V})G_a V_{\text{in}} & \text{for 021-models} \end{cases}$$

(\*): This expression assumes a  $50\,\Omega$  load, and depends on the individual unit power calibration. The actual output amplitude respects the maximum power limit set by the LIMIT command. The available modulation depth depends on the difference between the current output power (POW) and the predefined limit (LIMIT).

Similarly the gain required to achieve a desired modulation depth at 1 V input can be estimated as:

$$G_f = rac{1073709056}{250 \; ext{MHz}} df, \qquad G_\phi = rac{65536}{360^\circ} d\phi, \quad ext{and} \quad G_A = A_0 M_A,$$

where  $M_A$  is the amplitude modulation depth and  $A_0$  is the initial amplitude (returned by the POW command as a hexadecimal number).

Examples: when using a  $\pm 1 \, \text{V}$  modulation input,

- To change the frequency by  $\pm 1$  MHz, set the gain to  $1073709056 \times (1/250) = 4294836$ .

- To modulate the phase by  $\pm 45^{\circ}$ , set the gain to  $65536 \times (45/360) = 8192$ .

• To amplitude modulate by  $\pm 50\%$  in an ARF421 at an average RF power of +30 dBm, use the POW command to determine that the amplitude is 0x2000 = 8192, and set the gain to  $8192 \times 0.5 = 4096$ .

### 5.3 Dual modulation: fast and slow modes

The ARF/XRF is capable of dual modulation, where the RF is either simultaneously FM and AM or PM and AM modulated. However, due to DDS interface limitations, only one parameter can be modulated at full speed using the parallel bus. The other parameter is modulated on the serial bus at 1 MHz.

The FMSPEED command allows selection of which modulation parameter has higher bandwidth as shown in the table below.

| Command        | FM/PM bandwidth | AM bandwidth |

|----------------|-----------------|--------------|

| FMSPEED,1,FAST | 10 MHz          | 1 MHz        |

| FMSPEED,1,SLOW | 1 MHz           | 10 MHz       |

**Table 5.2:** Effect of using **FMSPEED** to control modulation on Channel 1.

The signal processing chain causes a propagation delay between the modulation input and the RF output of approximately 500 ns in fast (parallel) mode, and  $<3\,\mu s$  in slow (serial) mode. Furthermore, inducing a step change with slow modulation (e.g. using AM to switch the output) may appear to have jitter of up to 500 ns depending on the delay between the change in the modulation input and the subsequent DDS update.

Simultaneous FM and PM is not currently supported, as phase modulation shares the "FREQ" modulation input.

5.4 Examples 31

# 5.4 Examples

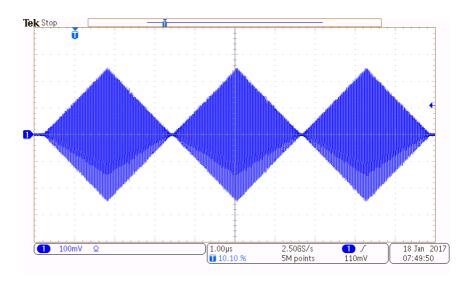

### 5.4.1 Simple linear ramps

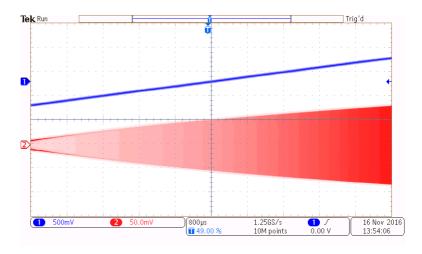

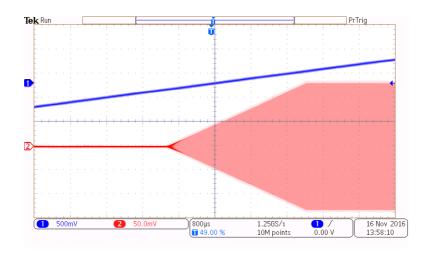

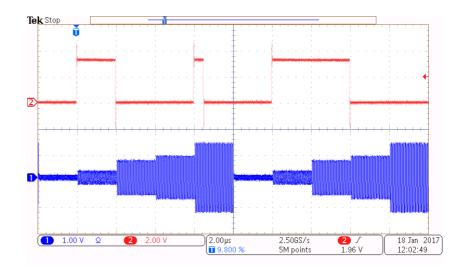

Listing 5.1 shows simultaneous linear ramping of amplitude and frequency (Figure 5.1). A linear ramp is connected to both the FREQ1 and AMPL1 modulation inputs in parallel. Subsequently increasing the AM gain results in clamping the amplitude to respect the limit set by the LIMIT command (Figure 5.2).

```

# configure the channel

FREQ,1,60MHz

POW,1,0dBm

LIM,1,10dBm

# connect linear ramp to FREQ1 and AMP1 mod in

MDN,1,AMPL,ON,4000

MDN,1,FREQ,ON,30000

FMSPEED,1,SLOW

```

Listing 5.1: Simultaneous AM and FM

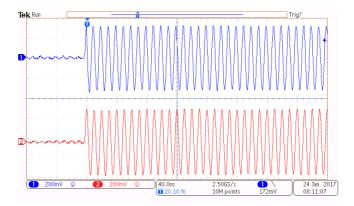

**Figure 5.1:** Demonstration of simultaneous AM/FM modulated RF (red) when driven by a linear ramp (blue).

**Figure 5.2:** Demonstration of high gain amplitude modulation showing clipping at zero and the power limit set by the **LIMIT** command.

### 5.4.2 Comparison of fast and slow modulation

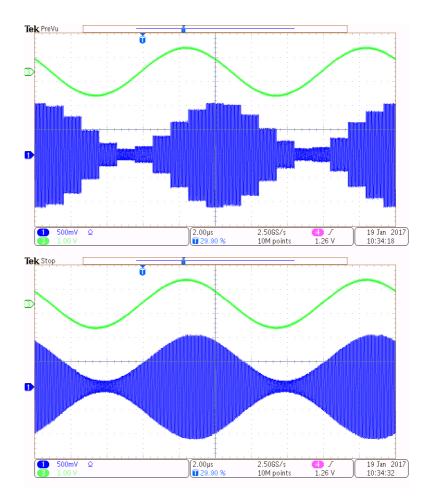

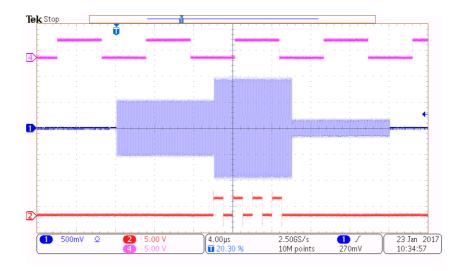

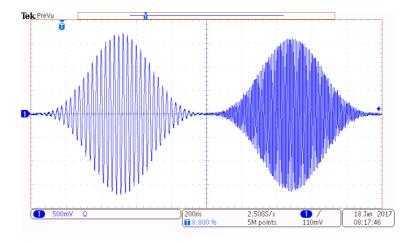

Figure 5.3 compares the result of different FMSPEED settings when applying a  $1\,V_{pp}$  sine wave at  $100\,kHz$  to the AM-input when both AM and FM are enabled simultaneously.

In this scenario, only one parameter can be applied to the fast parallel bus for maximum modulation rate. When FMSPEED is set to FAST, the amplitude is modulated via the slow serial interface, and the envelope displays stepwise discretisation.

Alternatively, when FMSPEED is SLOW, amplitude modulation uses the fast parallel interface and the resulting envelope is smoother at the expense of stepwise changes in frequency.

Although smooth changes in all parameters is desirable, depending on the application stepwise changes in one parameter may be acceptable provided smooth changes can be achieved in the other.

5.4 Examples 33

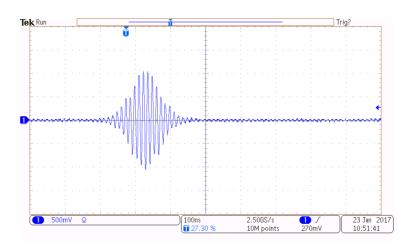

**Figure 5.3:** Comparison of the output waveform (blue) with FMSPEED, FAST (top) and FMSPEED, SLOW (bottom) when performing amplitude modulation with a 100 kHz sine-wave input (green).

### 5.4.3 Phase modulation

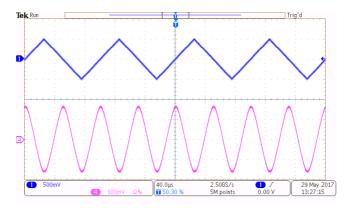

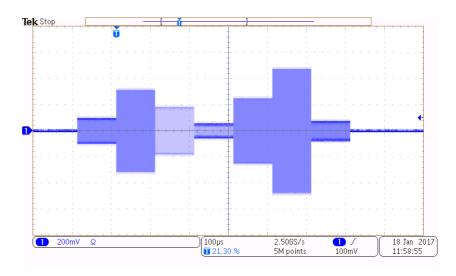

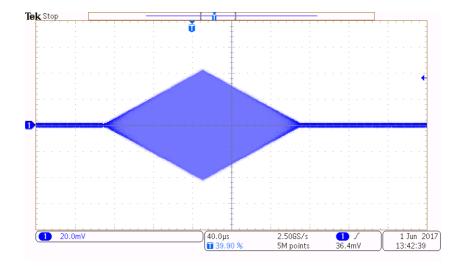

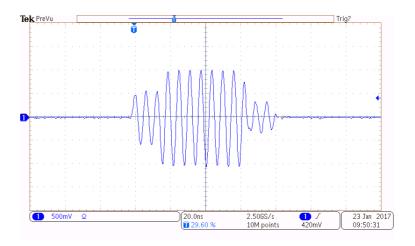

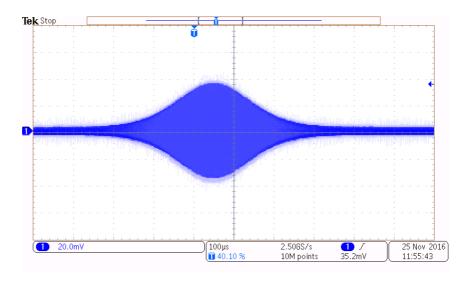

The two channels of the ARF/XRF can be used to perform phase modulation experiments whereby CH2 is used to demodulate CH1. Using phase modulation mode with a 1 Vpp modulation input with gain 0x7ffff gives  $\pm \pi$  phase modulation (Figure 5.4).

**Figure 5.4:** A 1 Vpp, 10 kHz triangle wave (blue) is used for phase modulation of CH1 and demodulated with an unmodulated CH2 at the same frequency (magenta).

Note that it may be necessary to adjust the phase of one of the channels using the PHAS command to compensate for the (frequency-dependent) differential phase delay in the signal paths and give a demodulated signal centred at zero. Similarly the SYNC feature should be enabled to ensure the two channels are phase-locked to each other.

# 6. PID stabilisation

In addition to external modulation, the ARF/XRF in NSB mode also implements PID control loops which can be used in conjunction with an AOM to perform intensity or frequency stabilisation of a laser. Each channel has an independent PID controller, which acts to drive an "error signal" provided to the modulation input towards zero.

Engaging the PID controller in amplitude mode adjusts the instantaneous RF output power, which could be used to compensate for the amplifier frequency response when performing wide-band frequency ramps, or to reduce the technical noise of a laser beam propagating through the AOM ("noise eating").

# 6.1 Signal conditioning

Upon engaging the PID controller, the associated modulation input SMA connector on the back-panel is treated as an "error signal" instead of a control voltage, and the action of the controller is to drive this signal towards zero. A DC shift can be applied using the PID, SETPOINT command to lock to a non-zero voltage, which is beneficial to applications such as intensity stabilisation where a photodetector measurement must be held at a fixed value.

However, the modulation input used to digitise the error signal has a  $\pm 1\,\mathrm{V}$  range and 12 bits of precision. Therefore to lock to a set-point outside this range requires external set-point analog subtraction. Furthermore, it is often desirable to apply analog gain to the error signal to make use of the full dynamic range of the ADC, and may be necessary in applications where the classical intensity noise of the laser needs to be suppressed.

This analog signal processing must be done externally to the AR-F/XRF, with bandwidth at least an order of magnitude greater than the desired effective bandwidth of amplitude stabilisation. A clamp-

ing circuit should be used to ensure that the signal fed into the ARF/XRF does not exceed the  $\pm 1\,\mathrm{V}$  modulation input tolerance, as this can damage the input ADCs.

For convenience, MOGLabs produces a signal-conditioning board (B3120) available as an optional extra, which provides:

- 1. Manual offset adjustment,  $\pm 10 \,\mathrm{V}$

- 2. Analog offset subtraction (e.g. from DAC output)

- 3. Variable analog gain

- 4. Monitor outputs for both photodetector and error signals

- 5. Output protection, to prevent exceeding  $\pm 1 \, \text{V}$ .

- 6. 10 MHz bandwidth

### 6.2 PID control loop

The ARF/XRF implements the feedback control via a standard PID (proportional integral differential) function:

$$u(t) = Gk_p e(t) + Gk_i \int_0^t e(\tau)d\tau + Gk_d \frac{de}{dt},$$

where e(t) is the input error signal, u(t) is the feedback response, and G is the overall modulation gain. The gain constants  $k_p$ ,  $k_i$ ,  $k_d$  are floating-point values in the range [0,1) which correspond to proportional, integral and differential terms respectively. Typical values are  $k_p = 0.03 - 0.8$ ,  $k_i = 0.01 - 0.15$  and  $k_d = 0$ .

Earlier versions of the firmware also included a distinct "anti-windup" gain, which has since been replaced by a saturating integrator for simplicity.

When optimising a PID control loop, it should be kept in mind that the achievable loop bandwidth is limited by the propagation delay of the entire signal processing chain, not just the modulation bandwidth. This includes the impulse response of the AOM, photodetector and signal-processing electronics, as well as the ARF/XRF.

### 6.3 Dual modulation with PID

It is possible to perform PID simultaneously with another form of modulation enabled. For example, PID can be used to compensate for the frequency response of RF components or the AOM when performing wide-band frequency modulation, as shown in Listing 6.1.

```

# enable FM on channel 1

MDN,1,FREQ,ON

GAIN,1,FREQ,Ox3FFFF

# set PID gains and enable

PID,GAIN,1,P,O.1

PID,GAIN,1,I,O.01

PID,GAIN,1,D,O

PID,ENABLE,1,AMPL

# set FM to SLOW mode, allowing PID to be FAST

FMSPEED,1,SLOW

```

**Listing 6.1:** Simultaneous FM and PID intensity stabilisation example.

Limitations of the DDS interface mean that only one of PID and external modulation can be performed at full bandwidth (§5.3). Most applications will benefit from using PID in "fast" mode, but some applications such as compensating for thermal drift in AOM diffraction efficiency do not require high bandwidth and can be operated in "slow" mode.

# 6.4 Noise-eater implementation

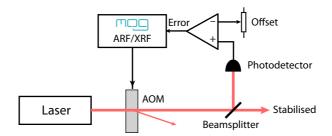

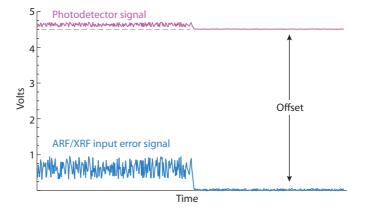

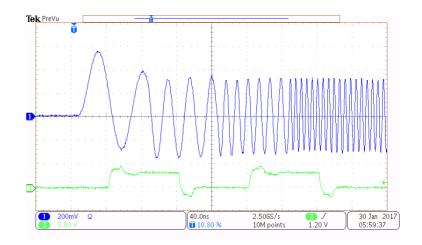

A common application for PID controllers is optical noise eating, which technical noise arising from power fluctuations in a laser beam. Figure 6.1 shows a typical configuration, where the intensity of the undiffracted (zero-order) beam is stabilised as seen in Figure 6.2.

In this configuration, the AOM acts as a high-speed variable optical attenuator, diffracting some of the light into the unused first-order output. The transmitted optical power is measured with a photodetector, and the ARF/XRF controls the RF power in proportion to the

**Figure 6.1:** Typical setup for optical power noise eater.

**Figure 6.2:** Photodetector signal (magneta) and conditioned error signal (blue) before and after activating noise-eater feedback (simulated). Note that the DC offset must be subtracted during signal conditioning.

6.5 Example 39

measured optical power. If the measured power is too high, the RF power is increased and more light is diverted into the diffracted output. This allows fluctuations in intensity to be suppressed, at the expense of reducing the transmitted power slightly (typically 90% transmission is achieved).

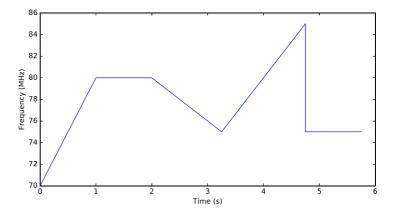

# 6.5 Example

The following example configures PID on Channel 1 for a particular set of gain constants. Note that the **gain constants must be tuned for each particular implementation**. Optimising the gain constants in real-time with the *Modulation settings* window in mogrf (§4.3.2) while monitoring the measured noise on a spectrum analyser is recommended for optimal performance.

```

# Setup channel 1 for PID noise—eater feedback

# set sample rate

PID, RATE, 1, 15.625

# set P, I, D, A gains

PID, GAIN, 1, P, 0.5

PID, GAIN, 1, I, 0.05

PID, GAIN, 1, D, O

# set overall gain

GAIN, 1, AMPL, 100

# set frequency and power

FREQ, 1,80MHz

POW, 1, 20dBm

# monitor u(t) on DAC output

PID, MON, 1, output

# activate AMPLITUDE control

PID, ENABLE, 1, AMPL

# check status

PID, STATUS, 1

```

# 7. Digital I/O

TTL digital inputs and outputs  $(0-5\,\text{V})$  are provided on the ARF/XRF through the DE15 connector on the rear panel, and the high-speed bus (HSB). The inputs can be used as triggers and the outputs can be controlled manually or using by table mode entries (§8.3).

**Note:** Digital inputs are pulled *high*, meaning that a disconnected input pin is equivalent to supplying a TTL high to that input.

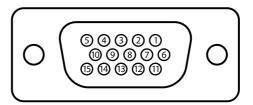

### 7.1 DE15 connector

The DE15 connector on the rear panel (Figure 7.1) provides both analogue and digital output for monitoring, and digital inputs for synchronisation purposes.

### CHx-AOUT Pin 11 (Ch1), Pin 13 (Ch2)

Analogue outputs for diagnostics and monitoring, controlled by the MOUT command. Note that the channel number here refers to the DAC channel, which is not necessarily the same as the RF channel.

### CHx-DOUT Pin 4 (Ch1), Pin 9 (Ch2)

TTL outputs that can be controlled manually or from table mode, for example to activate a mechanical optical shutter or trigger another device. This output has a rise time of 3 us.

**Note:** Pin 9 is internally disconnected in some commercial DE15 cables. Please ensure your cable has pin 9 continuity when using CH2-DOUT.

### CHx-SEQ Pin 3 (Ch1), Pin 5 (Ch2)

Pin used for hardware triggering in table mode. When the table is armed and a falling edge is received, the table begins executing. In REv2 units, this pin is not connected and the CHx-ON pin must be used instead.

| Pin | Signal     | Туре    |

|-----|------------|---------|

| 1   | CH1 OFF    | TTL in  |

| 2   | CH1 ON     | TTL in  |

| 3   | CH1 SEQ(*) | TTL in  |

| 4   | CH1 DOUT   | TTL out |

| 5   | CH2 SEQ(*) | TTL in  |

| 6   | CH2 ON     | TTL in  |

| 7   | CH2 OFF    | TTL in  |

| 8   | GND        | 0 V     |

| 9   | CH2 DOUT   | TTL out |

| 10  | GND        | 0 V     |

| 11  | CH1 AOUT   | ±2.5 V  |

| 12  | GND        | 0 V     |

| 13  | CH2 AOUT   | ±2.5 V  |

| 14  | GND        | 0 V     |

| 15  | GND        | 0 V     |

**Figure 7.1:** Pinout of high-density 15-pin female DE-style rear panel IO connector. Pins marked (\*) are not available in Rev2 units.

### CHx-ON Pin 2 (Ch1), Pin 6 (Ch2)

Driving this pin LOW in NSB mode instructs the FPGA to switch **ON** both the RF signal and amplifiers (if present). Has no effect if the output is already enabled. For applications that require the amplifiers to stay powered on, the CHx-OFF pin should be used instead. In Rev2 units, this pin acts the table mode trigger.

### CHx-OFF Pin 1 (Ch1), Pin 7 (Ch2)

This input bypasses the FPGA and directly turns the RF switch OFF unless a TTL LOW is provided. Bypassing the FPGA provides an extremely fast method for generating externally-controlled pulses, as further discussed in §7.6.

This pin is **disabled by default** and must be enabled using the EXTIO, ENABLE command. If enabled and the pin is disconnected, the RF output will not turn on.

# 7.2 High-speed digital

The FPGA also provides 16 high-speed digital I/O lines for use with table mode. Internal connector P1 accepts a 30-way, 0.50 mm pitch ribbon cable that can be inserted through a slot in the left-hand side of the case. The connector is an Omron XF2M-3015-1A, with example matching FFC ribbons Molex 0982660326 (150 mm length) or 0152660329 (200 mm length). Each line includes a series resistor  $(35\,\Omega/10\,\Omega~{\rm Rev2/Rev3+})$  and capability to sink and source 12 mA.

In Rev2 hardware, the high-speed lines are only usable as outputs and the DE15 connector must be used for inputs. In Rev3+ hardware, the high-speed lines can be configured as inputs or outputs using the EXTIO,MODE command, which configures groups of lines called "banks" (Table 7.1).

For example, to configure pins D1-D8 (bank 1) as inputs and pins D9-D16 (bank 2) as outputs, use the commands (Rev3+):

```

EXTIO, MODE, 1, HSB, READ EXTIO, MODE, 2, HSB, WRITE

```

**Figure 7.2:** High-speed digital IO connector (internal). Note that the FFC cable can be inserted upside-down, reversing the pin ordering.

B0

В1

B2

**B**3

27

28

29

30

GND

GND

**GND**

**GND**

17

18

19

20

| Version | Driver       | Bank size      | Example configuration  |  |  |  |

|---------|--------------|----------------|------------------------|--|--|--|

| Rev2    | 74LVT2244    | Outputs only   | 16x outputs            |  |  |  |

| Rev3-4  | 74LVTH2245   | Banks of 8     | 8x inputs, 8x outputs  |  |  |  |

| Rev5+   | 74LVTH162245 | Sub-banks of 4 | 4x inputs, 12x outputs |  |  |  |

Table 7.1: High-speed I/O configuration options

Rev5+ hardware can either configure the banks of 8 pins as above, or control sub-banks of 4 lines. For example to set pins D1-D4 (sub-bank 1A) as inputs and pins D5-D8 (sub-bank 1B) as outputs, use the command:

EXTIO, MODE, 1, HSB, READ, WRITE

7

8

9

10

A2

А3

GND

**GND**

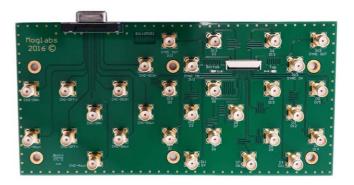

### 7.3 XSMA breakout board

The XSMA breakout board (Figure 7.3) is an optional additional component that provides SMA connectors for each of the digital I/O lines of both the DE15 connector (§7.1) and the high-speed bus (§7.2). The pins of the high-speed bus have matched track-lengths, to ensure consistent propagation delay for applications using advanced table mode.

**Figure 7.3:** XSMA digital I/O breakout board, providing SMA connectors for the DE15 connector (left) and high-speed digital connector (right).

The flat-flex cable (FFC) carrying the high-speed digital I/O signals can be inserted in either orientation, with contacts facing up or down. Each pin of the high-speed bus has two labels, corresponding to the purpose of the pin given the cable orientation.

If the orientation is the same within the ARF/XRF and the XSMA board, the second set of labels apply, whereas if the cable is crossed-over, the first set apply. Second-generation breakout boards include LED indicators labelled "Top" and "Bottom" that identify which set of labels to use.

The board dimensions are 172x70mm (first generation) or 172x85mm (second generation).

# 7.4 Configuration

The EXTIO command is used to control the behaviour of digital I/O. Outputs can be set with EXTIO, WRITE, and queried with EXTIO, READ when set to MANUAL control, or commanded by table mode entries when set to AUTOMATIC control.

The table below shows the functionality available on the different pins. Pins in the high-speed bus can be addressed individually (HSn) or collectively as a whole bank (HSBANK) in case multiple outputs need to be changed simultaneously. HSB is short-hand for HSBANK.

| Function | OFF          | ON/SEQ       | DOUT         | HSB          | HSn          |  |

|----------|--------------|--------------|--------------|--------------|--------------|--|

| Enable   | $\checkmark$ | -            | -            | $\checkmark$ | -            |  |

| Disable  | $\checkmark$ | -            | -            | $\checkmark$ | -            |  |

| Reset    | $\checkmark$ | -            | $\checkmark$ | $\checkmark$ | -            |  |

| Mode     | $\checkmark$ | -            | -            | $\checkmark$ | -            |  |

| Control  | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| Write    | -            | -            | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| Read     | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |  |

| Counter  | ✓            | -            | -            | -            | ✓            |  |

The different EXTIO commands are summarised below.

# EXTIO, ENABLE EXTIO, ENABLE, ch, pin

Enable the functionality of the specified pin on the given channel ch. If pin is HSB, the entire bank of pins is enabled.

# EXTIO, DISABLE, ch, pin

Disable the functionality of the specified pin.

# EXTIO, RESET, ch, pin

Resets the functionality of the specified pin to its default state.

### EXTIO, MODE, ch, pin, [mode]

Change the mode of the specified pin. If pin is HSB, then mode is

7.4 Configuration 47

> either READ or WRITE. If pin is OFF, then mode is either LATCH or TOGGLE. If pin is disabled, it is enabled first.

> In Rev5+ hardware, the sub-banks can be controlled using a second mode command. The first mode argument applies to lines 1–4 of the bank, and the second applies to lines 5–8.

### EXTIO, CONTROL

### EXTIO, CONTROL, ch, pin, [mode]

Sets the control of the specified pin. The parameter mode is either MAN[UAL] or AUTO[MATIC]. Pins must be set to AUTO mode to access them in table mode. If pin is HSB and the (sub)bank is not in write mode, the (sub)bank is changed to write mode first.

### EXTIO, WRITE EXTIO, WRITE, ch, pin, value

Write the specified value to the output pin. If pin is HSB, then value is an 8-bit number, whose bits correspond to the values to set on the pins of that bank. Otherwise value can be one of ON, OFF, 1 or 0. If the pin is not set to MANUAL control, it is changed to manual control first.

### EXTIO, READ, ch, pin

Reads the specified pin and returns its current state. If pin is HSB, then the returned value is an 8-bit hexadecimal number where each bit corresponds to the state of the corresponding line.

# EXTIO, COUNTER, ch, pin, cmd

The FPGA provides independent digital counters which can be activated on any pin configured as an input. The counters can be individually started, stopped or queried (see §7.7).

# 7.5 TTL switching

A versatile feature of the ARF/XRF is the ability to switch the RF in response to an external input such as a tactile switch or a TTL trigger for device synchronisation.

Each channels has two TTL inputs on the DE15 connector, labelled CHx-OFF and CHx-ON (see 7.1), that control whether the output is enabled or disabled as described below. Both of the inputs are active LOW and have no effect if pulled HIGH.

Each input has a debouncer circuit for use with tactile switches that can be enabled or disabled using the DEBOUNCE command. Note that activating the debouncer will introduce a small delay to changes in the input.

CHx-ON When the output is disabled, pulling this pin LOW will switch both the RF signal and amplifiers ON (NSB mode only). Has no effect when disconnected.

CHx-OFF When enabled (below), the RF signal will be disabled unless this pin is pulled LOW. If disconnected or pulled HIGH, no output is produced. Does not affect the RF amplifiers.

This CHx-OFF functionality disables the RF output **unless** the required input is provided, so it must be explicitly enabled using software commands. There are two modes of operation for this input as described below.

### EXTIO, MODE, 1, OFF, TOGGLE

Sets CHx-OFF to TOGGLE mode: the RF is off whenever the input is HIGH and the output is enabled whenever the input is LOW. Can be used for generating rapid externally-controlled pulses.

### EXTIO, MODE, 1, OFF, LATCH

Sets CHx-OFF to LATCH mode: if the OFF input goes HIGH, the output will be disabled and remain disabled. The output can then only be re-enabled by taking the input LOW and **then switching on the output** via software or the front-panel. This functionality can be used as part of an interlock system.

### EXTIO, ENABLE, 1, OFF

Enable the CHx-OFF behaviour, as previously configured by the EXTIO, MODE command.

### EXTIO, DISABLE, 1, OFF

Disable the CHx-OFF input, regular operation using the ON and OFF commands.

Please note that this setting *is* stored persistently and needs to be manually disabled when no longer desired. Furthermore, in Rev2 devices the CHx-ON input also serves dual-purpose as a trigger in table mode.

# 7.6 Pulse generation

**Note:** Early devices may require a minor hardware modification to achieve the performance described in this section. Furthermore, ensure that the debouncer is disabled using the **DEBOUNCE** command when generating pulses with TTL inputs.

There are several approaches to generating pulses using an ARF/XRF in NSB mode (normal operation): using the TTL inputs on the DE15 connector, or using amplitude modulation (AM). Note that the AM input tolerance is  $\pm 1\,\text{V}$  whereas the TTL inputs are  $5\,\text{V}$ -tolerant. Do not apply TTL voltage levels to the AM input.

Pulses can also be generated in a preprogrammed sequence using table mode (chapter 8). On ARF devices these pulses have a minimum duration of 1  $\mu$ s, whereas the XRF is capable of 16 ns pulses.

Note that the RF amplifiers are susceptible to thermal transients when powering on and off, causing the output power to fluctuate. Switching the amplifiers (e.g. using CHx-ON) may result in RF output within several milliseconds, but the output power may take some time to stabilise depending on how long the amplifiers were powered off. Switching the RF only (e.g. using CHx-OFF) is recommended to avoid transients.

| Method    | Transition | Time   |

|-----------|------------|--------|

| RF switch | 7_         | 25 ns  |

| RF switch | 上          | 30 ns  |

| RF amp    | 乙          | 2 s    |

| RF amp    | 厂          | 2 s    |

| AM (fast) |            | 500 ns |

| AM (slow) |            | < 3 us |

| DE15-ON   |            | 2 ms   |

| DE15-OFF  |            | 40 ns  |

**Table 7.2:** Typical on/off time delays for switching hardware components, and for different methods of pulse generation (debouncer disabled). The time given for amplifier transitions includes time for the output to stabilise, which may vary between hardware revisions.

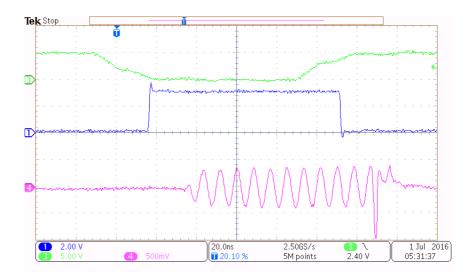

**Figure 7.4:** Modulation of RF output using the CHx-OFF input. Green is TTL signal at the source; blue is the TTL signal at the RF switch (internal to ARF); magenta is the RF signal.

*7.7 Counters* 51

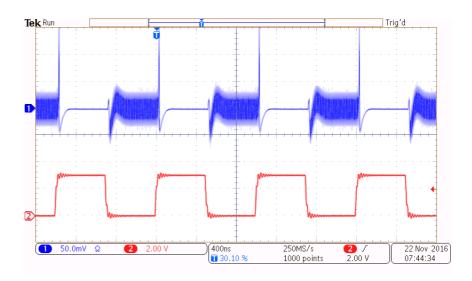

**Figure 7.5:** Example of pulse generation using the CHx-OFF input. Red is TTL signal; blue is the RF signal.

### 7.7 Counters

Fast digital counters can be accessed for each digital input pin. XRF devices can use these counters in advanced table mode ( $\S9.4$ ); ARF devices can only use them manually in scripts. To use a counter, the associated pin must be in READ mode and the counter function activated. The maximum edge-detection rate on the high-speed bus is 50 MHz, and level-detection (HIGH and LOW modes) accumulates 125 counts per microsecond.

The syntax to control counters is EXTIO, COUNTER, ch, pin, command, where command is one of the following:

READ, V[ALUE] Return the counter value as a 32-bit number

RESET, C[LEAR] Reset the counter value to zero

E[NABLE] Activate counter and begin accumulating count

D[ISABLE] Deactivate counter but hold count value

H[IGH] Count while input is HIGH, enables counter

L[OW] Count while input is LOW, enables counter

R[ISING] Count rising edges, enables counter

F[ALLING] Count falling edges, enables counter

B[OTH] Count both rising and falling edges, enables counter

The following NSB-mode example sets up a rising edge counter on HSB3 and counts for approximately 100 ms.<sup>1</sup>

```

EXTIO, MODE, 2, HSB, READ

EXTIO, COUNTER, 2, HS3, RISING

EXTIO, COUNTER, 2, HS3, RESET

SLEEP, 100 # wait approximately 100ms

EXTIO, COUNTER, 2, HS3, READ # returns counts recorded

```

# 7.8 Examples

The following examples demonstrate how to configure and use the external I/O pins. Note that pins must be set to MANUAL using the EXTIO, CTRL command to be used for READ and WRITE.

These commands may be useful in executing scripts or diagnosing experiments. For any application where timing is important, table mode should be used.

```

EXTIO, CTRL, 1, HSB, MAN

```

Set HSB1 to MANUAL mode, for use with READ and WRITE

```

EXTIO, WRITE, 1, DOUT, 1

```

Sets the CH1-DOut pin (DE15) to HIGH

```

EXTIO, READ, 2, OFF

```

Reads the current state of the CH2-OFF pin (DE15)

```

EXTIO, MODE, 1, HSB, WRITE

```

Set the entire first high-speed bank into write mode

<sup>&</sup>lt;sup>1</sup>Advanced table mode should be used for more accurate measurement (§9.4).

*7.8 Examples* 53

### EXTIO, WRITE, 1, HS7, ON

Sets port 7 of HSB1 to TTL HIGH

### EXTIO, WRITE, 1, HSB, 0x7

Simultaneously writes all pins in HSB1. Sets pins 0-2 HIGH and pins  $3\text{--}7\ \text{LOW}$

### EXTIO, MODE, 2, HSB, READ

Sets the entire second high-speed bank into read mode (only available in Rev3+ models)

### EXTIO, READ, 2, HSB

Simultaneously read all 8-inputs of the second HSB, and return the result as an 8-bit number

### EXTIO, READ, 2, HS3

Read only port 3 of HSB2 (returns "ON" or "OFF")

# 8. Simple table mode

Table mode performs sequential execution of up to 8191 instructions with precise timing. This enables generation of complicated pulse sequences, custom envelope shapes, and automated control of experiment sequences through digital I/O.

There are two versions of table mode: *simple* table mode (TSB mode) which utilises the DDS serial interface, and *advanced* table mode (TPA mode) that utilises the parallel interface. Advanced table mode has increased functionality and improved timing resolution, as described in chapter 9, and is only available in XRF devices.

# 8.1 Operational principle

A table is defined as a number of entries that describe the frequency, amplitude and phase of the rf output at each step, as well as any desired I/O. These are preloaded by the FPGA into a DDS "profile", so that when the sequence is executed the parameters are updated instantaneously. However, this makes table mode incompatible with both external modulation and PID control.

The speed of the serial interface limits the rate at which new instructions can be loaded into the DDS, so the duration of each table entry is discretised at  $1 \mu s$ .<sup>1</sup>

Once the sequence has been defined using the TABLE, ENTRY commands, it is readied for execution using the TABLE, ARM command. The table is checked for errors, and will fail if an incompatibility is detected. For example, to use digital output, the associated pin must be configured for AUTO control (§7.4).

Once the table is armed, execution is started by either a hardware

$<sup>^{1}\</sup>mbox{Advanced}$  table mode (XRF) is capable of 16 ns steps using the parallel bus.

TTL trigger on the SEQ input<sup>2</sup> or using the TABLE, START command. The phase-accumulator of the DDS is then reset and the table executes autonomously under FPGA control. This provides a very high degree of reproducibility in terms of both timing of instructions and output of the DDS generators, as the DDS phase accumulator is reset for every execution.

The table can be automatically restarted after completion by enabling the TABLE, RESTART option, and execution can be stopped midsequence using the TABLE, STOP command.

Each channel has its own independent table, and there are *slots* for four distinct tables in non-volatile memory. Commonly-used tables can then be stored on the device for later use. However, it should be noted that stored tables may become inoperable after a firmware upgrade and tables should be archived in human-readable form.

When a table is armed, the RF is switched on (including the amplifiers for 421-models), and upon completion of the table the final RF state remains ongoing. If it is required that the output be disabled when the table is complete, the final entry should set the power to 0x0 (zero amplitude, not  $0\,dBm$ ).

# 8.2 Defining table entries

Table entries can be defined or queried using the TABLE, ENTRY command. Once the entries have been set, the TABLE, ENTRIES command should be used to set the length of the table. Alternately, the TABLE, APPEND command can be used to add an entry to the end of the table and update the count automatically.